�}Ŀ�б�(�����𰸺ͽ���)

����ͬ�W(xu��)���п����팍(sh��)�(y��n)��ԇ�r������(li��n)�·늉�Ҏ(gu��)���M(j��n)����̽����

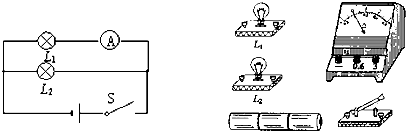

����ͬ�W(xu��)���п����팍(sh��)�(y��n)��ԇ�r������(li��n)�·늉�Ҏ(gu��)���M(j��n)����̽����| I1/A | I2/A | I/A |

| 0.2 | 0.2 | 0.4 |

����ͬ�W(xu��)���п����팍(sh��)�(y��n)��ԇ�r������(li��n)�·늉�Ҏ(gu��)���M(j��n)����̽����

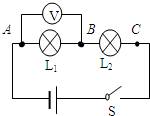

����ͬ�W(xu��)���п����팍(sh��)�(y��n)��ԇ�r������(li��n)�·늉�Ҏ(gu��)���M(j��n)����̽����| UAB/V | UBC/V | UAC/V |

| 2.4 | 1.4 | 3.8 |

| UAB | UBC | UAC |

| 1.5 | 1.4 | 2.9 |

����ͬ�W(xu��)���п����팍(sh��)�(y��n)��ԇ�r������(li��n)�·늉�Ҏ(gu��)���M(j��n)����̽����

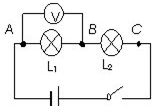

����ͬ�W(xu��)���п����팍(sh��)�(y��n)��ԇ�r������(li��n)�·늉�Ҏ(gu��)���M(j��n)����̽����| UAB/V | UBC/V | UAC/V |

| 2.4 | 1.4 | 3.75 |

����ͬ�W(xu��)���п����팍(sh��)�(y��n)��ԇ�r������(li��n)�·늉�Ҏ(gu��)���M(j��n)����̽����

����ͬ�W(xu��)���п����팍(sh��)�(y��n)��ԇ�r������(li��n)�·늉�Ҏ(gu��)���M(j��n)����̽����| UAB/V | UBC/V | UAC/V |

| 2.4 | 1.4 | 3.5 |

�ٶ����� - ����(x��)���б� - ԇ�}�б�

����ʡ��(li��n)�W(w��ng)�`���Ͳ�����Ϣ�e��ƽ�_ | �W(w��ng)���к���Ϣ�e�^(q��) | ����p�_�e�^(q��) | ��vʷ̓�o���x�к���Ϣ�e�^(q��) | �����֙�(qu��n)�e�^(q��)

�`���Ͳ�����Ϣ�e���Ԓ��027-86699610 �e���]�䣺58377363@163.com